RISC-Vは、由緒正しいハーバード大生まれのRISCアーキテチャーの第五世代。ライセンスフリーで自由に利用できるオープンかつ時代に合わせたチューニングによるハイパフォーマンスが特徴です。 以前32bit版で紹介しましたが、短くシンプルな16bitの縮小命令RV32Cを使って、Arm Cortex-M0学習用のasm15をRISC-Vに対応させたasm15rを設計。

そもそも、コンピューターとは何でしょう?

コンピューターとは、膨大な数を記憶し、正確かつ超高速に計算するものです。

どう記憶しどう計算するかを指示する数、それがマシン語。 CPUが違えばマシン語が違います。各メーカーによって系統があり、具体的なCPUによって使える命令が異なりますが、基本的はどれも一緒です。

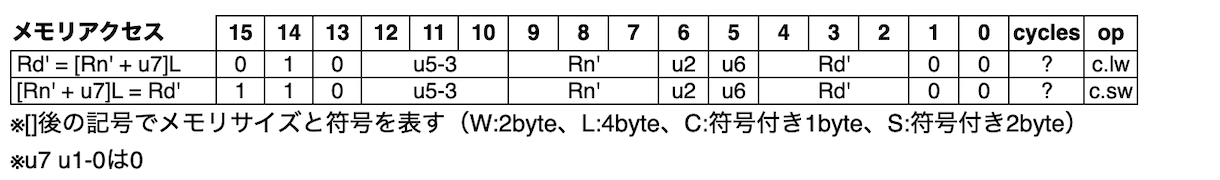

「RV32C RISC-Vマシン語表 (asm15r)」

こちらまとめたRISC-Vマシン語です(抜粋)

RISC-Vのラインナップは、32bit/64bit/128bitの大きく三種類。今回は入門しやすい32bitで縮小命令、掛け算割り算命令対応版をセレクト。

32bitコンピューターでの記憶は大きく2種類。数個から数十個ある32bit(4byte)のレジスタと呼ばれるものと、数KBから数GBまでのメモリ(RAMやROM)と呼ばれるもので記憶します。 RISCアーキテクチャでは計算はレジスタを使って行い、メモリとレジスタとのやり取りは別の命令で行います。

こちらがメモリとレジスタをやりとりする命令。

ここでRISC-Vを使った超シンプルなRISC-V 32bitコンピューターを仮定します。

1. メモリはアドレス0から始まる32byteのROM(16bitずつ16セットのスイッチで0/1切り替え可能、上下8bit入れ替え)

2. アドレス32から始まる4byte(32bit)には、対応する32コのLEDがついている(エンディアン入れ替え)

3. アドレス0から始めるリセットボタン

R10=1 R10+=1 R11=32 [R11]=R10

メモリアクセスにレジスタR8以降しか使えないので、計算もレジスタR10とR11を使うことにします。

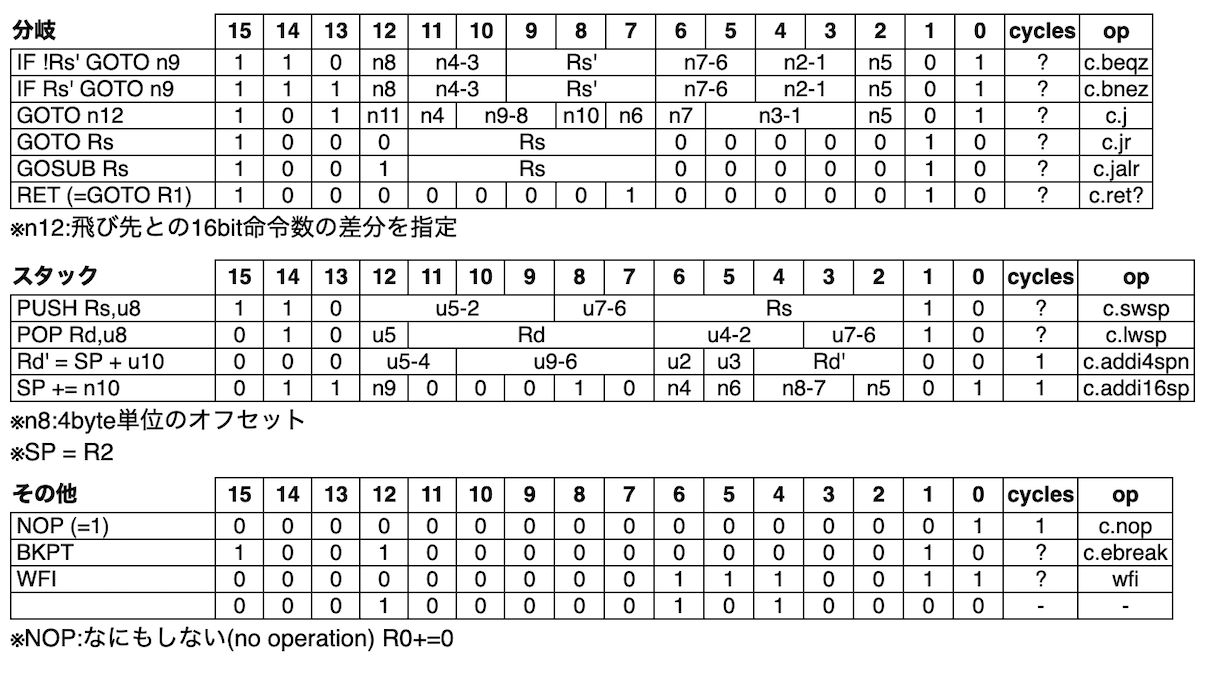

他にも、コンピューターにおいて大事な分岐や、複雑な計算の一時記憶に便利な機構スタックを実現する命令などが定義されています。

計算が終わった後もどんどん次のメモリを命令として実行していってしまうので、GOTO命令を使ってはじめに戻してあげましょう。

R10=1 R10+=1 R11=32 [R11+0]=R10 GOTO -4

この5つ、20byteの命令を命令表を見ながらビット列に置き換える、ハンドアセンブルし、スイッチを設定。(この作業を自動化するソフトがアセンブラやコンパイラ)

001 0 01010 00001 01 :'R10=1 000 0 01010 00001 01 :'R10+=1 001 1 01011 00000 01 :'R11=32 110 000 011 0 0 010 00 :'[R11+0]=R10 101 1 1 11 1 1 1 100 1 0 1 :'GOTO -4

これでLEDの右から2つ目だけが光って、1+1の計算結果が2であることを出してくれるプログラム、完成です!

スイッチをいじって、2+1の計算などにしてみましょう。

この架空のコンピューター、作ってみたくなりますね!

RISC-Vは誰もがオープンに使えるアーキテクチャ、また本ブログもCC BYのオープンデータ、自由に作って遊んだり売ったりして、OKです!

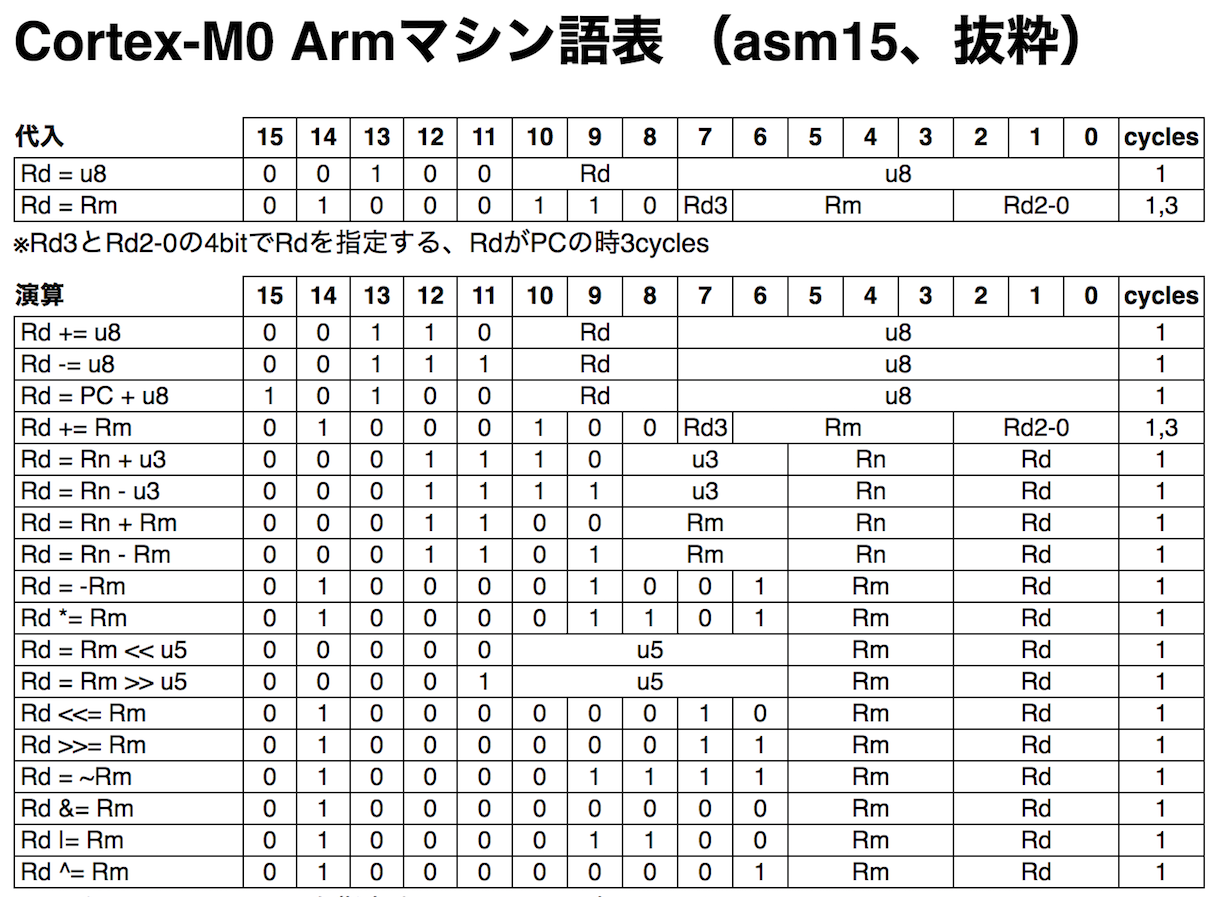

Armは、スマホや、IchigoJam、開発中の日本のスパコン富岳など、世界で最も普及しているCPUアーキテクチャ。Armの一番シンプルなCortex-M0のマシン語と比較してみましょう。

「Cortex-M0 Armマシン語表 (asm15)」

こちらも16bitが基本、似てますね。RISC-Vの縮小命令は32bitの標準命令と下位2bitで区別できるので混在できるのが特徴です。(RISC-Vの縮小命令には掛け算割り算がないので、32bit命令を使用)

Cortex-M0はレジスタ16本(プログラムカウンター含む)、RISC-Vは32本(内R0は0固定、プログラムカウンターは別)など、細かな違いの理由に思いを馳せるのもまた一興。

IchigoJamで、いますぐ遊べるマシン語の世界もぜひどうぞ!

「はじめてのマシン語 - IchigoJamではじめるArmマシン語その1」